Université de Béjaia Faculté des sciences exactes Département de mathématique Niveau Licence 1 Examen de rattrapage Structure Machine 2 Durée : 1h30 15 Décembre 2020 de 14h à 15h30

## Corrigé

| Chanitra 1 | · Circuite Iogiques | combinatoires – CLC   | Leur 11 5 points  |

|------------|---------------------|-----------------------|-------------------|

| cnabitre i | : Circuits logiques | s combinatoires – CLC | (SUF 11.5 DOINES) |

| Q1: CLC ( <i>sur 0.s por</i><br>□Dé <del>multiplexeur</del><br>□Afficheur 7 segmen<br>□Bascule | □ <del>Décodeur</del><br>ts □Registre | les composants ci-dessous  Additionneur  Mémoire  maire vers code gray | □Compteur<br>□Comparateur                                 | Indication : Tous doit |

|------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|------------------------|

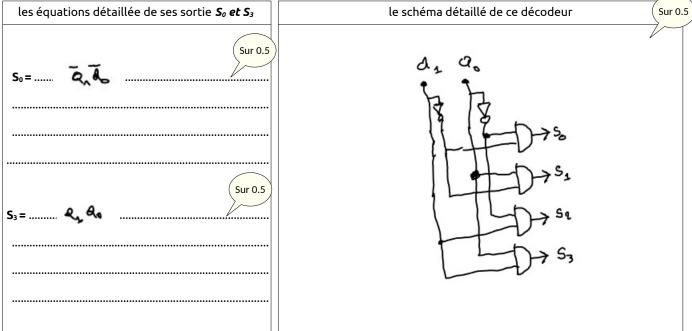

| validation <b>E</b> . Donnez                                                                   | <del>-</del>                          | odeur ayant 2 entrées de s                                             | sélection (adresse) ( <b>a</b><br>chéma détaillé de ce dé |                        |

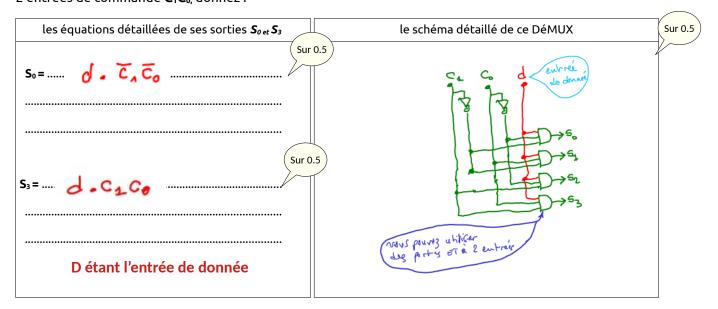

Q3: Démultiplexeur sur 1.5 points : Soit un DéMUX ayant 2 entrées de commande  $C_1C_0$ , donnez :

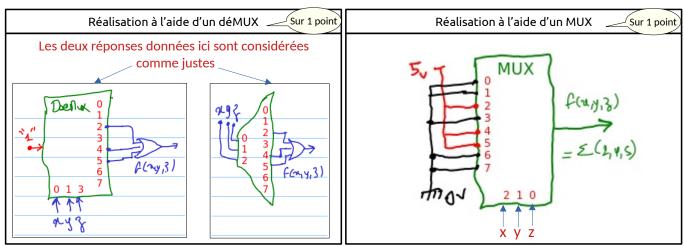

Q4: Réalisation de fonctions à l'aide de multiplexeurs et de démultiplexeur s ur 2 points : En vous servant d'un décodeur (ou DéMUX) puis d'un multiplexeur, donnez le schéma de réalisation de la fonction  $f(x,y,z) = \sum (2,4,5)$

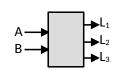

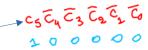

**Q5 : Faire la synthèse d'un circuit** (*sur 2 points*) . On vous demande de faire la synthèse d'un circuit qui permet d'indiquer le numéro codé par les entrées *A* et *B*. Ainsi, lorsque (AB) = (00), les sorties (L3, L2 et L1) sont toutes égales à « 0 ». Li (i allant de 1 à 3) est à « 1 » si code formé par les entrées A et B est i.

Q6: DéMUX (1 point). J'ai un DéMUX ayant 6 entrées de commande ( $c_5c_4c_3c_2c_1c_0$ ) et une entrée de donnée D.

A – Combien de sorties possède ce DéMUX?  $2^6 = 64$  sorties

A - Donnez l'expression algébrique détaillée de sa sortie  $S_{32}$ :

Q7: MUX (sur 0.5 point). J'ai un multiplexeur ayant 2 entrées de commande ( $c_1c_0$ ). S = do C.Co + do C.Co+do C.Co+do C.Co Donnez l'expression algébrique détaillée de sa sortie S:

Q8: DEC (sur 0.5 point). Soit un DEC à 4 entrées ( $e_3e_2,e_1e_0$ ), SL= Ezezezes donnez l'expression algébrique détaillée de sa sortie  $S_6$ :

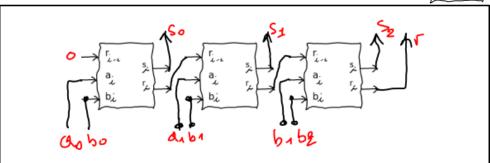

Q9: ADD (sur 1 point). Donnez les équations des sorties d'un étage additionneur complet

di @ (bi @ vi)

(Dis bi) ri-1 + aibin

Q10: ADD (sur 1 point).

En vous servant uniquement de l'étage additionneur de la question précédente, donnez le montage d'un addition 3 bits

Chapitre 2 : Circuits logiques séquentiels (sur 8.5 points)

Q11 - Bascule JK synchrone au niveau bas de l'horloge H (sur 1 point) : Indiquez ce qui se passe lorsque :

H=0 et J = K = 0: Mémorisation

H=1 et J=1 et K=0: Mémorisation

H=1 et J=0 et k=1: Mémorisation

Mémorisation H=1 et J=K=1:

La bascule étant sensible au niveau BAS implique que lorsque H=1, elle se met en état de mémorisation

Si H=0. elle devient sensible à ses entrées, et si J=K=O alors elle se met en état de mémorisation

Dans tous les cas la bascule est en état de mémorisation

Attention, votre réponse doit être entièrement correcte pour avoir 1 point

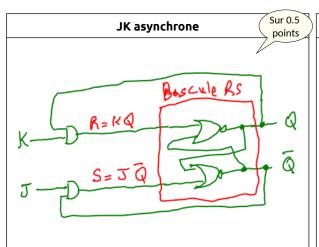

Q12 - Bascule RS (sur 1 points) : Donnez les schémas détaillés des bascules suivantes

Ne donnez pas le détail de la bascule JK

Q13 - Synchronisation (sur 2 **points)**: Citez les 4 types de synchronisation des bascules (relativement à une horloge H)

Synchronisation au niveau haut de H Synchronisation au niveau bas de H Synchronisation au front montant de H Synchronisation au front descendant de H

Chaque bonne réponse sur 0.5 point

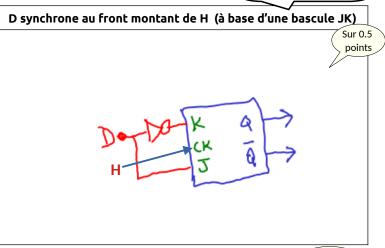

## Q14 - Bascule JK (sur 1.5 points):

A - Donnez le schéma d'une bascule JK Ck sensible au niveau bas d'une l'horloge H Les entrées J et K de cette bascule sont mise toutes les deux à « 1 »!

**B** – Que passe-t-il lorsqu'on met l'entrée H à 1?

La bascule se met en état de mémorisation

**C** – Que passe-t-il lorsqu'on met l'entrée H à 0?

La bascule se met en état de complémentation

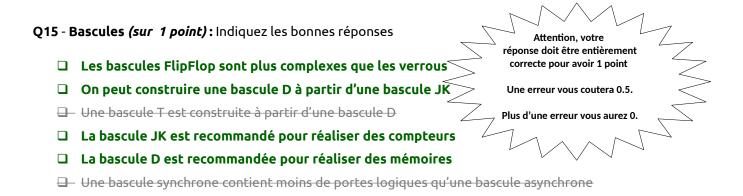

☐ Les bascules Latch sont différentes des verrous

☐ On peut réaliser la bascule RS à l'aide de portes NAND

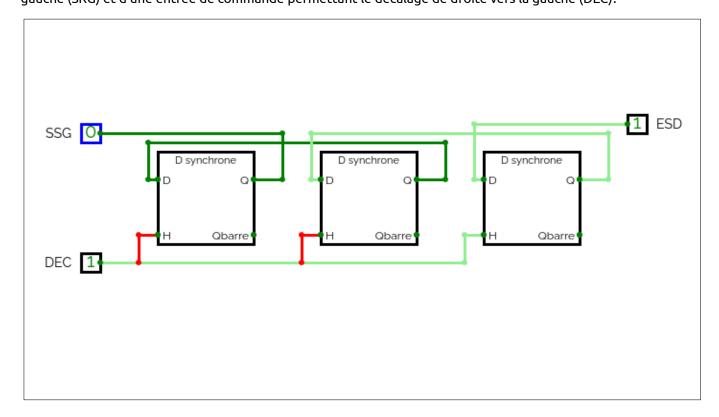

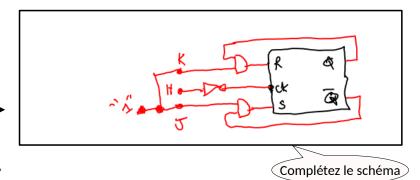

Q16 - Registre (sur 2 points) : Donnez le schéma logique d'un registre à décalage de droite vers la gauche. Ce

registre doit mémoriser **3 bits** d'information. Il doit disposer d'une entrée Série droite (ESD), d'une sortie série gauche (SRG) et d'une entrée de commande permettant le décalage de droite vers la gauche (DEC).