## Structure Machine 2 Série de TD1

https://elearning.univ-bejaia.dz/course/view.php?id=5349

Circuits logiques combinatoire (partie1)

### Séance de TD n°1

**Objectif**: Comprendre les fondements de la conception de circuits logiques combinatoires (CLC) et identifier les 2 grandes catégories de circuits logiques tout en expliquant le principe des circuits logiques combinatoires. Les étudiants, devraient aussi être capables d'énumérer les 3 classes de CLC et de citer quelques exemples de circuits dans chacune de ces classes. Enfin, il devraient être capables de faire l'analyse et la synthèse d'un CLC simple.

Q1 : Indiquez les étapes de conception des circuits logiques combinatoires (CLC)

Q2: Indiquez les 2 grandes catégories de circuits logiques existants

Q3 : Expliquer la différence entre « analyse » et « synthèse » d'un circuit logique

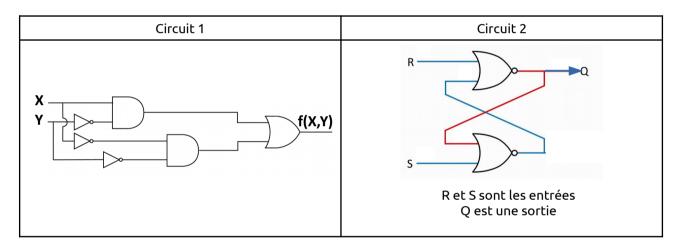

Q4: Indiquez si les circuits ci-dessous sont des CLC? Justifiez votre réponse:

Q5 – Citez 3 classes circuits logiques combinatoires (CLC)

Q6 – Citez 3 exemples de CLC permettant la transmission de données

Q7 – Citez 3 exemples de CLC permettant le calcul arithmétique et logique

Q8 – Citez 3 exemples de CLC permettant la conversion de code

### **Q9** – Analyser le circuits suivant :

C F

Je rappel qu'il s'agit d'identifier les équations des soties de votre circuit et d'essayer ensuite de simplifier!

**Q10** – Faire la synthèse d'un circuit de détection de débordement. Je vous renvoi au cours du premier semestre pour vous revoir la problématique de débordement de capacité lors des calculs arithmétiques. Je rappel juste qu'il s'agit de dire si un débordement se produit à l'issue d'un calcul entre deux nombres A et B. Vous devez vous basez sur les signes des 2 nombres A et B et sur le signe du résultats R du calcul entre A et B. Je vous rappel aussi qu'il faut appliquer la méthode de conception de CLC (cerner le problème en identifiant les variables et les fonctions, établir la TV, extraire la FCD, simplifier puis dessiner le logigramme). A vous de jouer!

# Structure Machine 2 Série de TD1

Circuits logiques combinatoire (Partie 2)

#### Séance n°2

**Objectif**: A l'issue de cette séance de TD, les étudiants devraient être capables de faire la synthèse de quelques circuits logiques combinatoires en se basant sur une spécification d'un problème. De plus ils doivent être capables d'effectuer un montage en cascades de circuits logiques combinatoires (détecteur d'erreur).

**Q11**: Faire la synthèse d'un circuit de détection de débordement de capacité : On vous rappel que le débordement se produits lors des calculs au sein des unités de calcul des ordinateurs. Si vous avez deux nombres A et B de même signe et vous leur appliquer un calcul (addition notamment), si vous obtenez un résultat avec un signe contraire aux deux nombres A et B, alors vous pouvez déduire que vous avez une situation de débordement. A vous de concevoir, à base de ce fait un circuit logique permettant d'indiquer cette situation de débordement!

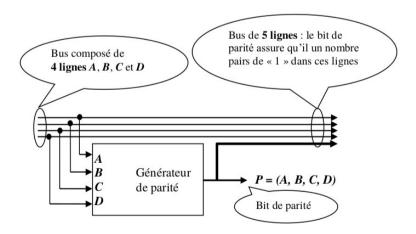

**Q12**: Faire la synthèse d'un circuits générateur de parité : On supposera qu'un générateur de parité est définit comme un circuit logique permettant d'assurer que le nombre de lignes à « 1 » dans un bus soit **toujours pair**. En supposant que vous avez un bus composé de 4 lignes ( $\bf A$ ,  $\bf B$ ,  $\bf C$  et  $\bf D$ ), le générateur de parité ajoute à ce bus une  $\bf 5^{\rm ème}$  ligne nommé «  $\bf P$  » dont l'état logique est positionné de sorte à garantir un nombre pair « 1 » dans ce bus. Nous rappelons qu'un bus est un ensemble de fils qui transportent chacun un bit d'information.

Q13: Faire la synthèse d'un circuits de détection d'erreurs sur un bus de transmissions de données. On supposera que dans ce bus on a assuré, à l'émission, que le nombre de « 1 » est pair. Bien évidement si la transmission s'est déroulée correctement, le nombre de « 1 » dans le bus restera à « 1 » à la réception sauf si une erreur s'est produits lors de la communication. A vous concevoir ce détecteur d'erreur pour un bus de 3 bits (2 bits de données et un bit de parité) puis pour un bus de 4 bits. Enfin vous devez proposer un détecteur d'erreur pour un bus de n+1 bits (n bits pour les données et 1 bit de parité).

**Objectifs des séances 3 et 4**: A l'issue des séances de TD 3 et 4, les étudiants devraient être capables de faire la synthèse de quelques circuits logiques combinatoires et d'effectuer des montages en cascades (comparateur, décodeur). Enfin, ils doivent aussi être capable de générer des fonction quelconques en utilisant des décodeur et des démultiplexeurs.

### Séance n°3

**Q14**: Dessiner un circuit additionneur de 2 mots A et B de 4 bits chacun (on met à votre disposition des 1/2 additionneur des des additionneurs complets)

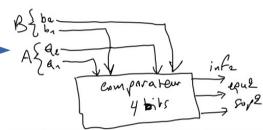

Q15: Faire la synthèse d'un comparateur entre 2 bits. On vous indique qu'un comparateur 2 bits doit avoir deux entrées (b1 et b2) et 3 sorites : inf1, sup1 et equ1. Voir le schéma suivant :

**Q16**: Faire la synthèse d'un comparateur entre **4 bits** en vous basant sur un comparateur 2 bits de la question précédente

**Q17**: <u>Généralisation</u>: Faire la synthèse d'un comparateur entre n bits en vous basant sur un comparateur 2 bits de la question précédente

### Séance n°4

**Q18**: Faire la synthèse d'un décodeur  $3 \Rightarrow 8$  à base de décodeur  $2 \Rightarrow 4$  **Q19**: Générer la fonction  $F(x,y,z) = \sum (1,5,6)$  à base de DEC et DeMUX