# **Structure Machine 2**

# Corrigé de la série de TD2

#### Séance de TD n°1

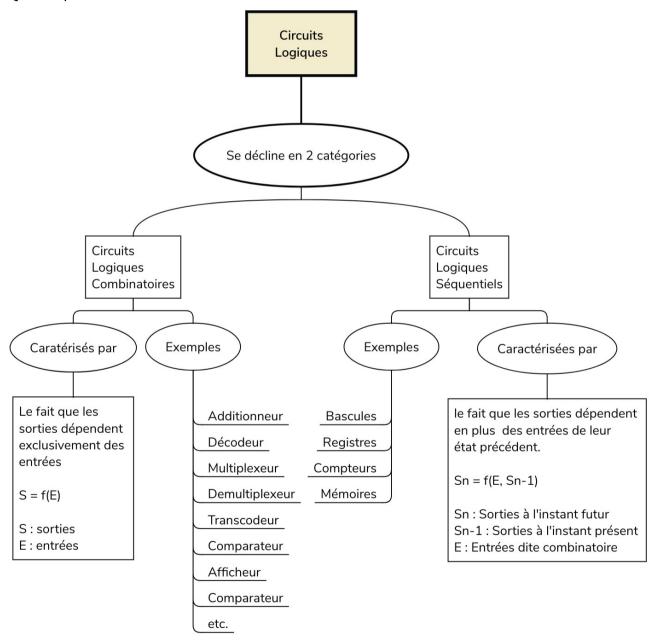

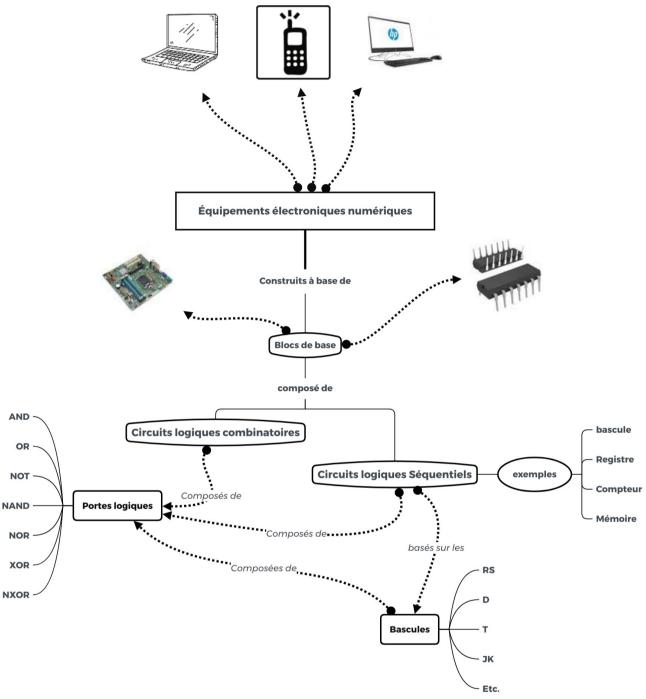

**Objectif**: Comprendre les fondements des circuits logiques de façons générale et celui des circuits logiques séquentiels en particulier. Expliquer le fonctionnement des différentes bascules RS, RSH, D, T, et JK.

#### Q1: Complétez le schéma suivant:

### Q1 : Complétez le schéma suivant :

Q3: On distingue 2 types de circuits logiques séquentiels :

Asynchrones

synchrones

**Q4:** Dans un circuits logiques asynchrone, on se sert d'un signal d'horloge pour faire coïncider les moments d'écriture des informations dans les bascules :

Vrai

Faux

**Q5:** Dans un circuits logiques synchrone, on se sert d'un signal d'horloge pour synchroniser les moments de changement d'état des bascules : ✓ **Vrai** □ Faux

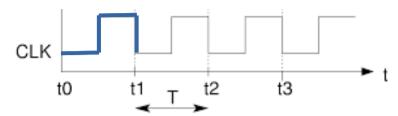

#### **06:** Dans le schéma suivant

- 1. Que représente CLK et T : Un signal d'horloge

- Quelle sont les grandeurs pour de mesurer CLK: Temps d'une période « T » ou fréquence « F ». La fréquence est l'inverse de la période: F = 1/T. Le temps est mesuré en seconde. La fréquence est mesuré en Hertz (Hz). La mesure actuelle de la fréquence d'horloge des microprocesseurs est de quelques GHZ (Giga hertz).

- 3. Surlignez sur le schéma une période d'horloge

4. Que veut dire la valeur 3 GHZ : 3 Giga Hertz, ce qui veut dire 3 x 10<sup>12</sup> Hz ou 3 milliards de Hz ou 3 milliards cycles d'horloges par secondes. En terme de temps ça équivaut 3x10-9 secondes ou 3 picot-secondes.

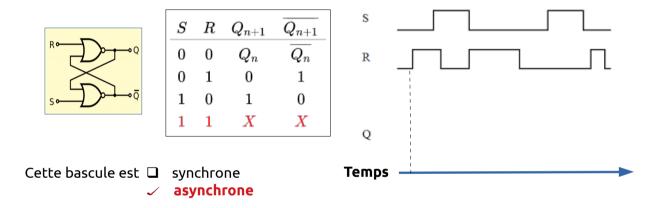

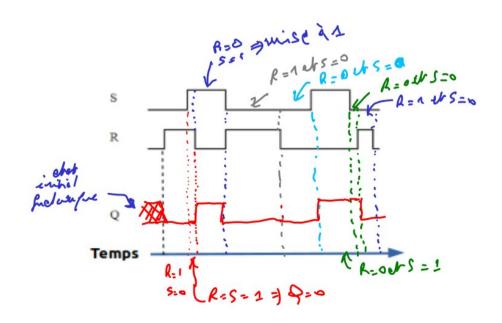

Q7 : Soit la bascule RS suivante, complétez sa table de vérité et le logigramme ci-dessous :

### réponse :

# Q8: Complétez le schéma suivant :

#### Séance de TD n°2

Objectif: Expliquer le fonctionnement des différentes bascules RSH, D, T, et JK.

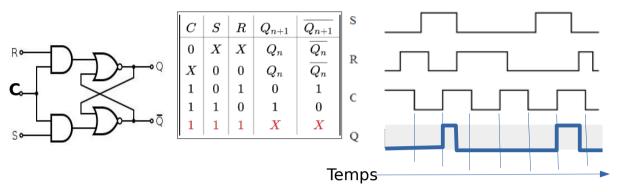

Q9 : Soit la bascule RSH suivante, complétez sa table de vérité et le logigramme ci-dessous :

Cette bascule est ✓ **synchrone** □ asynchrone

Q10: Pourquoi nous ne devrons pas mettre les entrées R et S à « 1 » au même temps ? Lorsqu'on met R=S=1, les sorties Q et  $Q_{barre}$  seront égales à 0 toutes les deux. Lorsqu'on passe à l'état de mémorisation (R=S=0), la bascule devient instable (On ne pourra pas dire avec certitude son état).

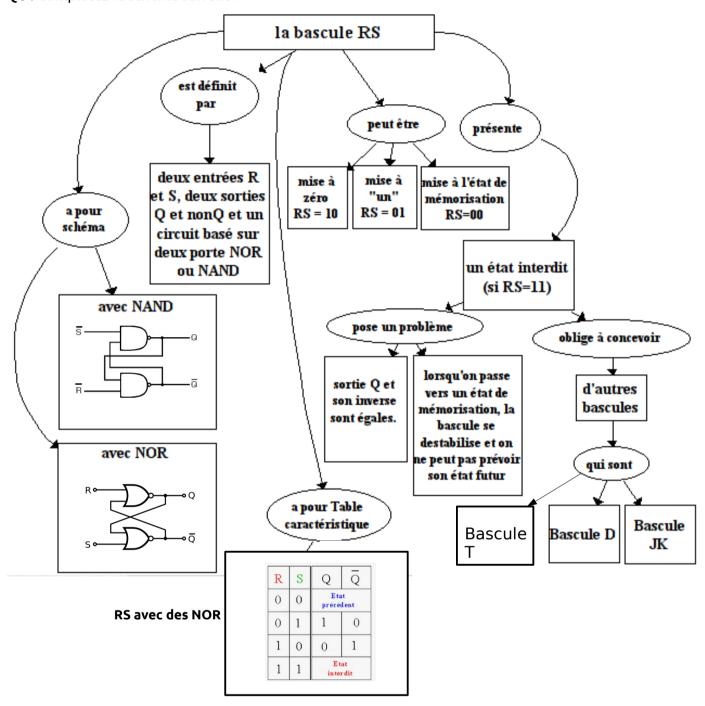

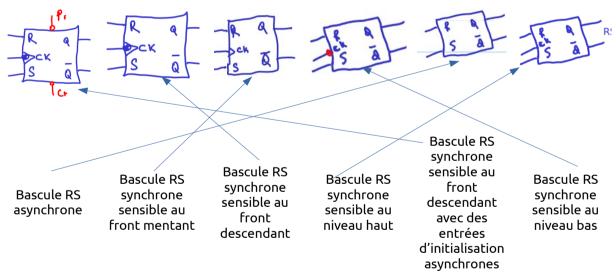

Q11: Reliez les schémas des bascules RS suivantes à leurs bonnes définitions :

**Q12:** Bascule T: Donnez le schéma d'une bascules « T » sensible au front montant de l'horloge

Complétez sa table de vérité:

| T | Н       | Qn                                     | Qn                            | remarque     |

|---|---------|----------------------------------------|-------------------------------|--------------|

| 1 | 7       | $\overline{\textbf{Q}_{\textbf{n-1}}}$ | Q <sub>n-1</sub>              | basculement  |

| 1 | 0,1,    | Q <sub>n-1</sub>                       | $\overline{\mathbf{Q_{n-1}}}$ | mémorisation |

| 0 | 0,1,  \ | Q <sub>n-1</sub>                       | $\overline{\mathbf{Q_{n-1}}}$ | mémorisation |

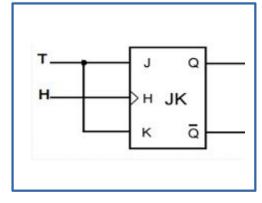

## Q13: Bascule JK: Soit la bascule JK représentée par la schéma suivant :

#### A - Cette bascule

- 1. est-elle synchrone ou asynchrone ? Synchrone

- 2. Est-elle sensible au front d'horloge ? front d'horloge

- 3. Est-elle sensible au front montant de l'horloge ? Front descendant d'horloge

B - Complétez sa table caractéristique : On voit que J et K sont reliés à Vcc (tension positive) donc ils sont à « 1 » tous les deux :

| Н       | Q <sub>n+1</sub> | Effet           |  |

|---------|------------------|-----------------|--|

| 0, 1, 🗷 | Qn               | Mémorisation    |  |

| 7       | Qn               | Complémentation |  |

→ : Front montant

↘ : Front descendant

### B - Complétez le logigramme suivant :

# Q14: Bascule D

A - Donnez le schéma d'une bascule D synchrone sensible au **niveau d'horloge haut** et basée sur une bascule RS.

B - Cette bascule est-elle appelée « verrous » ou flip-fplop?

## Réponse : Elle est appelée verrous

C – Complétez sa table de vérité:

| Н | D | J K | Q <sub>n+1</sub> | Effet        |  |

|---|---|-----|------------------|--------------|--|

| 0 | Х | хх  | Qn               | Mémorisation |  |

| 1 | 0 | 0 1 | 0                | Mise à zéro  |  |

| 1 | 1 | 1 0 | 1                | Mise à « 1 » |  |

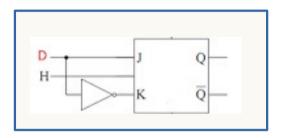

D – complétez le logigramme suivant

#### Séance de TD n°3

**Objectif**: Utilisez les bascules D et JK pour réaliser des compteurs et des registres.

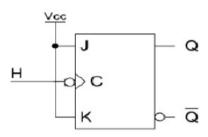

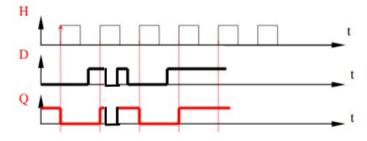

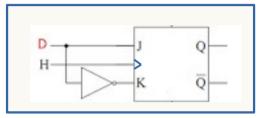

### Q15: Bascule D

A - Donnez le schéma d'une bascule D synchrone sensible au **front d'horloge haut** et basée sur une bascule JK.

B - Cette bascule est-elle appelée « verrous » ou flip-fplop?

### Réponse: Flip-Flop

C – Complétez sa table de vérité :

| Н          | D | J K | Q <sub>n+1</sub> | Effet        |

|------------|---|-----|------------------|--------------|

| 0, 1,<br>\ | Х | хх  | Qn               | Mémorisation |

| 7          | 0 | 0 1 | 0                | Mise à zéro  |

| 7          | 1 | 1 0 | 1                | Mise à « 1 » |

→ : Front montant

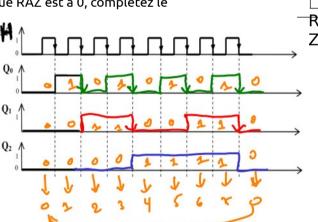

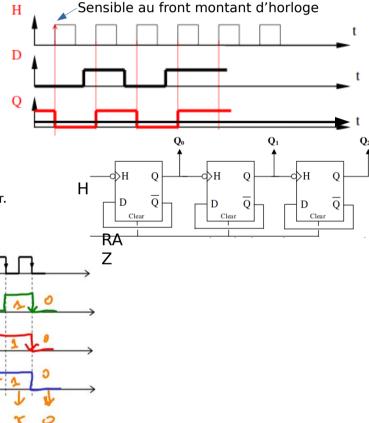

**Q16** – Compteur : Soit le schéma suivant

RAZ à « 1 » permet de remettre à zéro le compteur.

En supposant que RAZ est à 0, complétez le

logigramme suivant

D – complétez le logigramme suivant

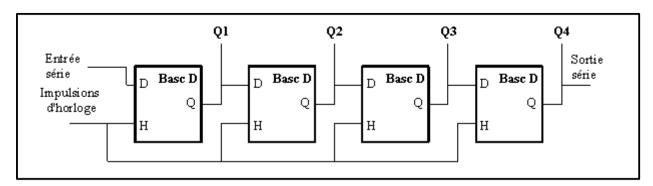

**Q17** – Donnez le schéma d'un registre à décalage de gauche à droite en utilisant des bascules D synchrones sensibles au front montant.

### Q18 – les circuits suivants représentent quoi?

Réponse : Registre à décalage gauche vers droite synchrone (car toutes les bascules ont le même signal d'horloge) avec sorites parallèle et une sortie série à droite. Ces bascules sont sensibles au niveau d'horloge haut.

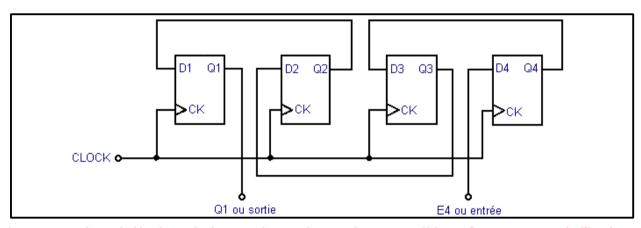

Réponse : Registre à décalage droite vers la gauche synchrone sensible au front montant de l'horloge

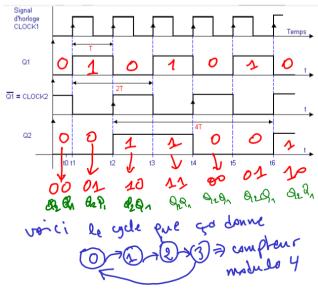

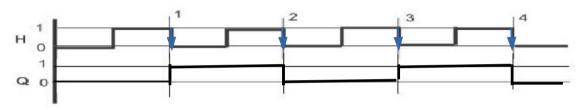

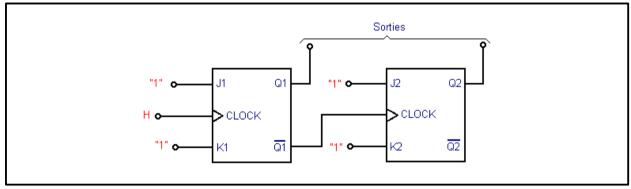

**Réponse**: Il s'agit de dire ce que fait le circuit exactement comme il est donnée. Ici nous avons deux bascules JK sensible toutes les deux au front montant de leurs entrées d'horloges respectives. La premier bascule s'inverse à chaque front montant de l'horloge H. La seconde s'inverse à chaque front montant de la sortie Qbarre de la première bascule.

L'analyse du chronogramme représentant le fonctionnement de notre circuit révèle clairement qu'il s 'agit d'un compteur module 4.