Université de Béjaia Faculté des sciences exactes Département MI Licence 1

EMD Structure Machine 2 Durée : 1h30 19 Juin 2019

Corrigé

## Chapitre 1: Circuits logiques combinatoires sur 12.5 points

Question1: CLC sur 1.5 point:

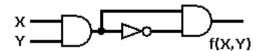

• Le circuit ci-dessus est-il un circuit logique séquentiel (justifier votre réponse)?

Ce circuit n'est pas séquentiel car sa sortie ne dépend que de ses entrées x et y. Elle ne dépend pas de l'état précédent des sorties.

- Donnez l'équation de f(x,y). (x, y) , v.y

- Pouvez-vous simplifier cette fonction, si oui donnez sa nouvelle expression : OUI f(x,y) = 0

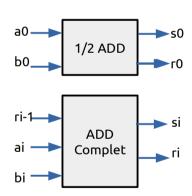

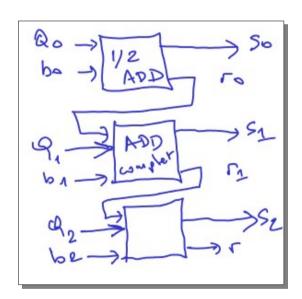

**Question2 :** Additionneur sur 0.5 point : En vous basant sur les circuits demi-additionneur et additionneurs complets cidessous, donnez le schéma de montage en cascade d'un additionneur 3 bits.

**Question3 : Décodeur** *sur 1 point* : En supposant que vous avez un décodeur à trois entrées *x*, *y* et *z*. la variable *x* représente le poids fort alors que *z* représente le poids faible. On suppose que ce décodeur ne dispose pas d'entrée de validation.

- Combien de sorties possède ce décodeur ? 2<sup>3</sup> = 8 sorties

- Donnez l'équation de la sortie  $S_6$ :  $S_6 = M_6 = 9293$

Question4 : Démultiplexeur sur 1 point : On vous rappel qu'un démultiplexeur possède une seule entrée de données et plusieurs sorties. Si vous avez un DeMUX ayant 2 entrées de commande (sélection) **x** et **y** et une entrée de validation *E*.

Combien de sorties possède ce DeMUX ?  $2^2 = 4$  sorties

Entrée de Entrée de validation donnée

Donnez l'équation de la sortie  $S_2$ :  $S_2 = E.D.m_1$

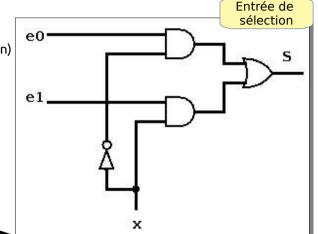

Question5: Multiplexeur sur 1.5 point: Si vous avez un multiplexeur ayant une seule entrée de commande (sélection)  $\boldsymbol{x}$  et  $\boldsymbol{N}$  entrées de données (e<sub>0</sub>, ...) et une seule sortie  $\boldsymbol{S}$ . On suppose qu'il n'y a pas d'entrée de validation.

- Combien vaut  $N: 2^1 = 2$  entrées

- Donnez l'équation e **S**:

5= mo. go + my e1 五分十九日

Donnez le schéma détaillé de ce MUX : •

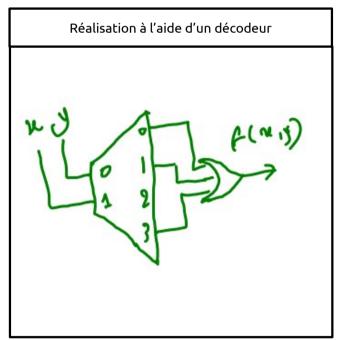

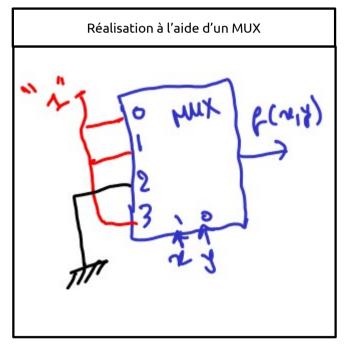

Question6: Réalisation de fonctions à l'aide de multiplexeurs et de décodeurs sur 1 point: En vous servant d'un décodeur puis d'un multiplexeur, donnez le schéma de réalisation de la fonction  $f(x,y) = \sum_{i=1}^{n} (0,1,3)$

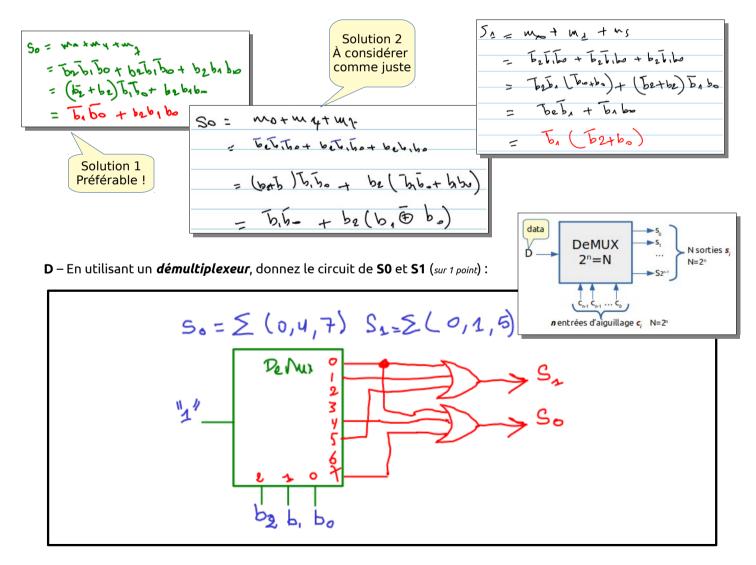

Question7: Faire la synthèse d'un Circuit Logique Combinatoire sur 6 points: En vous demande de faire la synthèse d'un circuit de transcodage permettant de garantir un codage des nombres (de 0 à 7) de sorte à ce qu'il y ait toujours 2 bits à « 1 ». On supposera que vous avez en entrée 3 bits (b2,b1,b0) et en sortie 5 bits (s4, s3, s2, s1, s0). Voici comment on souhaite le transcodage :

| 000 → 00011 | 001 → 00110 | 010 → 01100 | 011 → 11000 |

|-------------|-------------|-------------|-------------|

| 100 → 00101 | 101 → 01010 | 110 → 10100 | 111 → 10001 |

|    | Nom | ı :   |    | •••••  | ••••• |                     | ••••• |       | Prénom                                                                           | Groupe :             |

|----|-----|-------|----|--------|-------|---------------------|-------|-------|----------------------------------------------------------------------------------|----------------------|

|    |     |       |    | able d |       | ité ré <sub>l</sub> | ponda | ınt à | <b>B</b> – Donnez les expressions algébriques sorties ( <i>sur 2.5 points</i> ): | (FCD) de chacune des |

| ſ  | Е   | ntrée | es |        | 9     | ortie               | S     |       | S0 = <b>m0 + m4 + m7</b>                                                         |                      |

| ſ  | b2  | b1    | Ь0 | s4     | s3    | s2                  | s1    | s0    | 1                                                                                |                      |

| 10 | 0   | 0     | 0  | 0      | 0     | 0                   | 1     | 1     | S1 = m0 + m1 + m5                                                                |                      |

| 1  | 0   | 0     | 1  | 0      | 0     | 1                   | 1     | 0     | 1                                                                                |                      |

| 12 | 0   | 1     | 0  | 0      | 1     | 1                   | 0     | 0     | S2 = m1 + m2 + m4 + m6                                                           |                      |

| 13 | 0   | 1     | 1  | 1      | 1     | 0                   | 0     | 0     | 32 - 111 + 1112 + 1114 + 1116                                                    |                      |

| 14 | 1   | 0     | 0  | 0      | 0     | 1                   | 0     | 1     | 1                                                                                |                      |

| 15 | 1   | 0     | 1  | 0      | 1     | 0                   | 1     | 0     | S3 = <b>m2 + m3 + m5</b>                                                         |                      |

| 16 | 1   | 1     | 0  | 1      | 0     | 1                   | 0     | 0     | 1                                                                                |                      |

| 17 | 1   | 1     | 1  | 1      | 0     | 0                   | 0     | 1     | S4 = <b>m3 + m6 + m7</b>                                                         |                      |

| Ī  |     |       |    | 1      |       |                     |       |       | 1                                                                                |                      |

C - Simplifiez algébriquement les expressions des sorites SO, S1 et S2(sur 2 point):

# Chapitre 2 : Circuits logiques séquentiels sur 6.5 points

### Question 8 - Compteurs (sur 1.5 points):

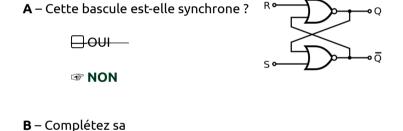

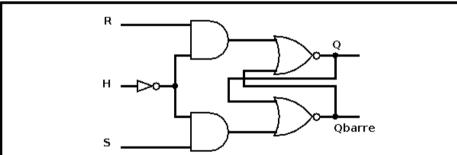

Question 9 - Bascule RS sur 1 point: Soit la bascule RS suivante:

table de vérité

| R | S | $\mathbf{Q}_{n}$ | $Q_{n+1}$ | Observation    |

|---|---|------------------|-----------|----------------|

| 0 | 0 | 0                | 0         | Memorisation   |

| 0 | 0 | 1                | 1         | MEWIGHTS A NOV |

| 0 | 1 | 0                | ۴         | Nise à "1"     |

| 0 | 1 | 1                | þ         | Thise a 2      |

| 1 | 0 | 0                | 0         | الناع هُ "ال   |

| 1 | 0 | 1                | င         | INE & o        |

| 1 | 1 | 0                | X         | etat intendit  |

| 1 | 1 | 1                | ×         | or at the fact |

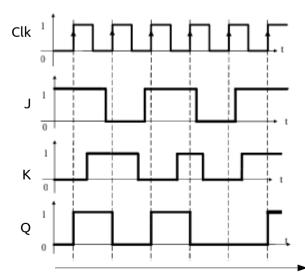

Question 10 - Bascule JK synchrone sensible au front montant (sur 1 point): Complétez la table de vérité et le chronogramme suivant :

| Entrées                          | 5 |   | 05.1 | Fonctionnement  |

|----------------------------------|---|---|------|-----------------|

| Clk                              | J | K | Qn+1 | Fonctionnement  |

| 0 ou 1 ou<br>front<br>descendant | Х | х | Qn   | Mémorisation    |

|                                  | 0 | 0 | Qn   | Mémorisation    |

| Front                            | 0 | 1 | 0    | Mise à zéro     |

| montant                          | 1 | 0 | 1    | Mise à 1        |

|                                  | 1 | 1 | Qn   | Complémentation |

| 110111 : |

|----------|

|----------|

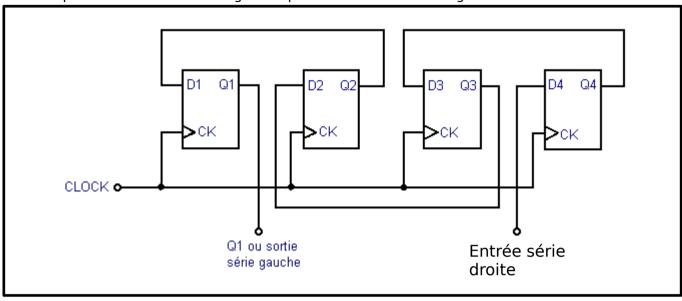

**Question 11 - Registre (sur 1 point):** En vous basant sur la bascule **D synchrone au front montant**. Donnez le schéma d'un registre à décalage de droite vers la gauche avec une entrée série droite et une sortie série gauche. Ce circuit permet de réaliser un décalage à chaque front montant de l'horloge :

Question 12 - Bascule RS synchrone (sur 1 point): Donnez le schéma détaillé d'une bascule RS sensible au niveau d'horloge bas (utilisez des portes NOR):

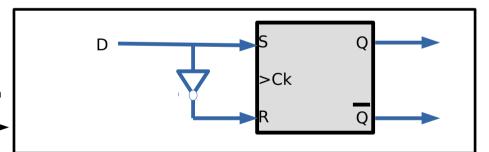

Question 13 - bascule D (sur 1 point): En vous basant sur une bascule RS sensible au front d'horloge haut, donnez le schéma d'une bascule D sensible au front d'horloge haut.

### Chapitre 3 : Circuits intégrés sur 1 point

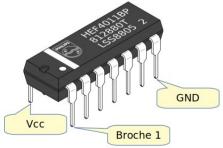

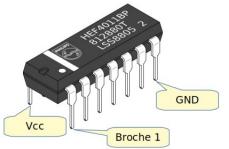

**Question 14 -** Sur le circuit intégré suivant, indiquez la broche **n°1**, la broche correspondant à **VCC** (source de tension) et celle correspondant à **GND** (masse).

Consignes de notation : chaque erreur vaut -0.5 point)

## Explications plus détaillées

#### A propos de la question 8

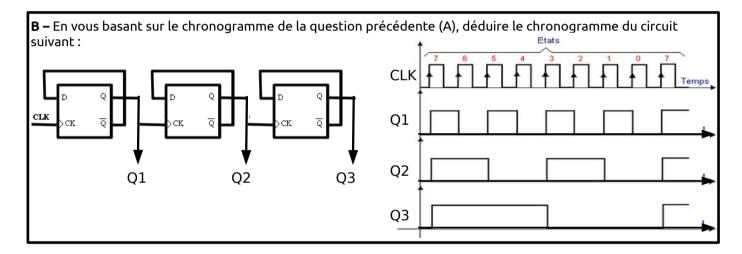

Question 8 - Compteurs (sur 1.5 points):

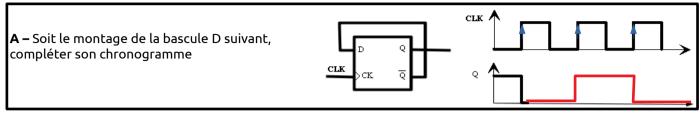

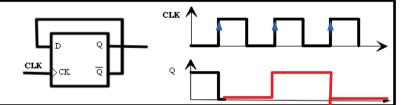

**A –** Soit le montage de la bascule D suivant, compléter son chronogramme

- Ici nous avons à faire à une bascule D (flip-flop) sensible au front haut de l'horloge

- Comme l'entrée D = Qbarre, à chaque front montant de l'horloge, on écrira Qbarre dans la bascule

- Ceci va nous donner le chronogramme indiqué ci-dessus : On voit que le signale Q a une période 2 fois plus grande que le signal d'horloge. On dira qu'il s'agit d'un diviseur de fréquence.

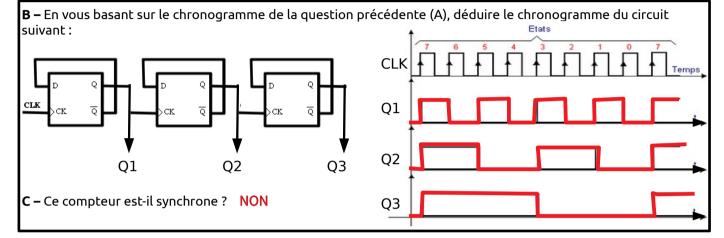

Le montage en cascade du diviseur de fréquence de la question A en faisant de sorte que la sortie Qi soit l'entrée d'horloge de l'étage suivant, alors on obtiendra à chaque sortie d'un étage i un diviseur de fréquence de l'étage précédent. (Diviseur de fréquence veut dire que a période sera doublé, c'est ce qui nous donne le chronogramme de la question B

C – Ce compteur est-il synchrone? NON. En effet, un compteur synchrone se caractérise par le fait que toutes ces bascules sont reliées au même signale d'horloge. Dans le cas de notre circuit, cette situation ne se présente pas, donc notre compteur n'est synchrone.

A propos de la question 14: Tous les circuits intégrés dispose d'une coche et éventuellement d'un repère (un rond ou un point). Cette coche et ce rond permettent de trouver facilement la broche n°1. Sur la même rangée que la broche 1 à l'autre bout se trouve la broche qui doit être reliée à la masse (GND) et parallèlement la broche 1 sur l'autre rangé se trouve la broche qui doit être reliée à la tension VCC.