Université de Béjaia Faculté des sciences exactes Département de mathématique Niveau Licence 1

Examen de Structure Machine 2 Durée : 1h30 26 Juin 2021 de 12h30 à 14h00

Corrigé

### Chapitre 1 : Circuits logiques combinatoires – CLC (sur 10,5 points)

#### Q1: Distinguer entre CLC et CLS (1 point): Cochez les bonnes affirmations:

- un CLC rempli une fonction de mémorisation

- les sorties d'un CLC ne dépendent pas de leurs état précédent

- ☐ les sorties d'un CLS dépendent uniquement des entrées combinatoires

- les sorties d'un CLC dépendent de leurs entrées combinatoires et de leur état précédent

- ☐ Une bascule est un CLC

- □ un registre est un CLS

- □ un compteur est un CLC

- ☐ On utilise des chronogrammes pour analyser des CLS

- □ Un décodeur est un CLC

Indication: chaque erreur coûtera 0.5 points

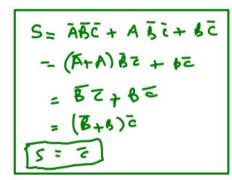

## Q2: Analyse d'un circuit logique (sur 1 point) : Effectuez l'analyse du circuit suivant :

On voit que la sortie de ce circuit est Charre

# Q3 - Différencier entre décodeur (DEC), multiplexeur (MUX) et démultiplexeur (DéMUX) (sur 3 points). Complétez le texte suivant :

- Un DEC est un circuit ayant n entrées d'adresse et 2<sup>n</sup> sorties et possiblement une entrée de validation E.

En ignorant son entrée de validation, l'équation de chacune de ses sorties Si est donnée par la formule suivante

S<sub>i</sub> = m<sub>i</sub> avec m<sub>i</sub> le minterme i composé des variables d'entrée.

- Un DeMUX est un circuit ayant n entrées de commande, une entrée de données, et 2<sup>n</sup> sorties et possiblement une entrée de validation E. En ignorant son entrée de validation, l'équation de chacune de ses sorties Si est donnée par la formule suivante

$S_i = D.m_i$  avec  $m_i$  le minterme i composé des variables de commande ......

• Un MUX est un circuit ayant *n* entrées de commande, **2**<sup>n</sup> entrées de données, et **une** sortie et possiblement une entrée de validation *E*. En ignorant son entrée de validation, l'équation de sa sortie *S* est données par la formule suivante :

${\it e}_i$  : les entrées de données et  ${\it m}_i$  : mintermes des variables de commande

**Indication**: chaque erreur coûtera 0,5 point

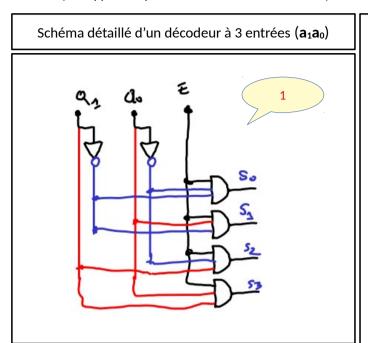

**Q4 – Décodeur** (sur 2 points): Donner le schéma détaillé d'un décodeur à 2 entrées ( $\mathbf{a}_1\mathbf{a}_0$ ) puis donnez les équations de ses sorties  $S_i$  (on supposera qu'on a une entrée de validation  $\mathbf{E}$ )

$a_0 \, \big| \, b_0 \, \big| \, s_0 \, \big| \, r_0$

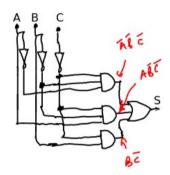

**Q5 : Réalisation de fonctions à l'aide de multiplexeurs et de décodeurs s**ur 3,5 points : En vous servant d'un décodeur puis d'un multiplexeur, donnez le schéma de réalisation de la fonction demi-soustracteur (opération de soustraction binaire entre 2 bits) ayant pour entrées :  $a_0$  et  $b_0$  et comme sorties :  $s_0$  (la somme) et  $r_0$ (la retenue).

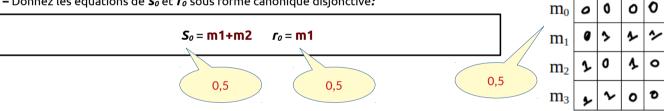

**A** – Donnez la table de vérité des fonctions  $\mathbf{s}_0$  et  $\mathbf{r}_0$

**B** – Donnez les équations de  $s_0$  et  $r_0$  sous forme canonique disjonctive:

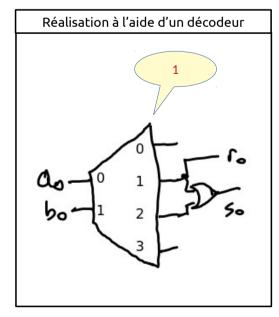

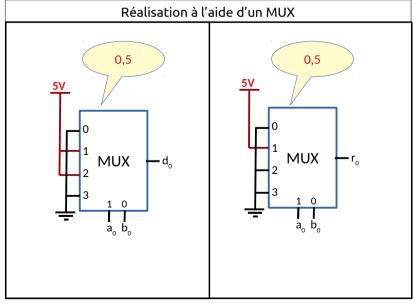

C – Donnez le logigramme de s₀ et r₀ en utilisant d'abord un décodeur puis un MUX (un MUX possède une seule sortie)

# Chapitre 2 : Circuits logiques séquentiels (sur 9,5 points)

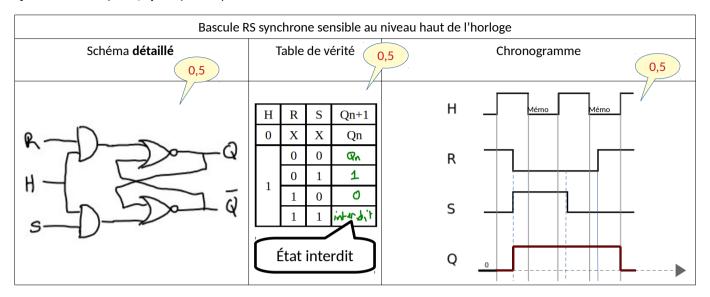

### Q6 - Bascule RS (sur 1,5 point) : Complétez le tableau suivant

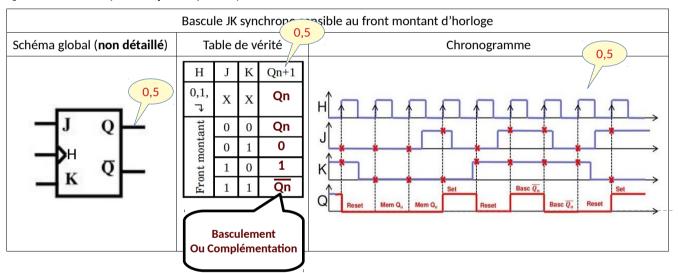

# Q7 - Bascule JK (sur 1.5 points) : Complétez le tableau suivant

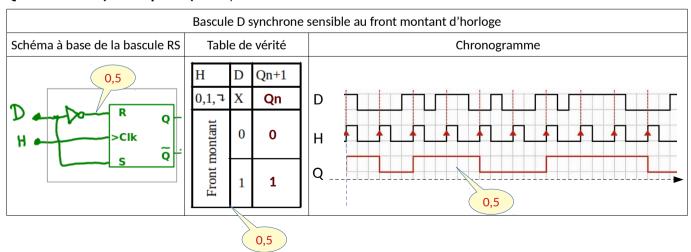

# Q8 - Bascule D (sur 1.5 points): Complétez le tableau suivant

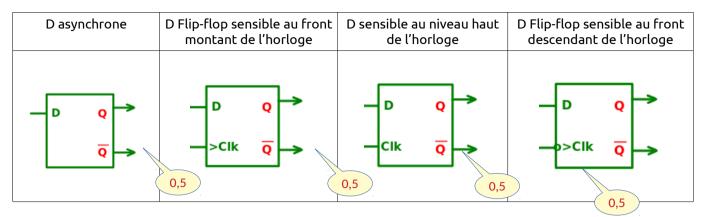

#### Q9 - Synchronisation (sur 2 points): Donnez les schémas (globaux) des bascule D suivantes :

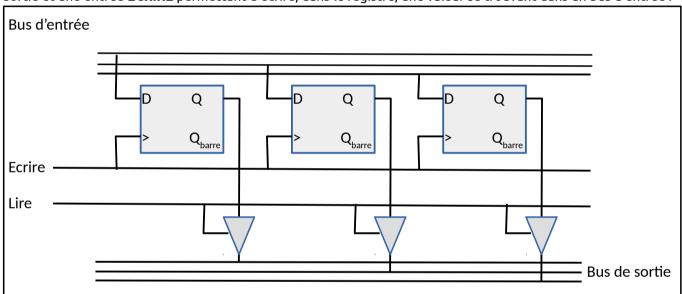

**Q10** - **Registre** (sur 2 points): En utilisant des bascules **D** synchrones sensibles au front montant, donnez le schéma d'un registre (3 bits) doté d'une entrées *LIRE* permettant de lire le contenu du registre dans le bus de sortie et une entrée *ECRIRE* permettant d'écrire, dans le registre, une valeur se trouvant dans un bus d'entrée :

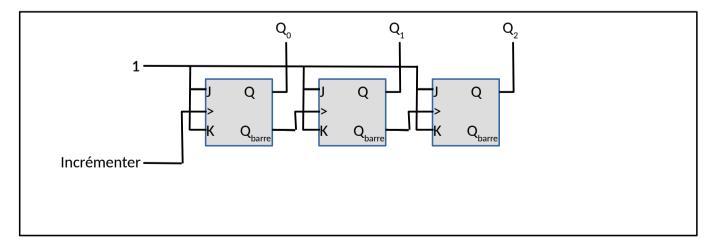

**Q11** - **Compteur** (sur 1,5 point): En utilisant des bascules **JK synchrones sensibles au front montant**, donnez le schéma d'un compteur modulo 7.